#### US005276716A

# United States Patent [19]

#### Wincn

[11] Patent Number:

5,276,716

[45] Date of Patent:

Jan. 4, 1994

| [54] | BI-PHASE<br>IN CMOS | DECODER PHASE-LOCK LOOP                           |

|------|---------------------|---------------------------------------------------|

| [75] | Inventor:           | John M. Winen, Cupertino, Calif.                  |

| [73] | Assignee:           | Advanced Micro Devices Inc.,<br>Sunnyvale, Calif. |

| [21] | Appl. No.:          | 595,522                                           |

| [22] | Filed:              | Oct. 11, 1990                                     |

|      |                     |                                                   |

## Related U.S. Application Data

| [63] | Continuation-in-part of Ser. No. 480,426, Feb. 15, 1990, and a continuation-in-part of Ser. No. 595,068, Oct. 10, |  |  |

|------|-------------------------------------------------------------------------------------------------------------------|--|--|

|      |                                                                                                                   |  |  |

|      | 1990, Pat. No. 5,164,960.                                                                                         |  |  |

| [51] | Int. Cl. <sup>5</sup> | H03D 3/24         |

|------|-----------------------|-------------------|

| [52] | U.S. Cl               | 375/120; 375/119; |

|      |                       | 331/1 A           |

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,259,644 | 3/1981  | Iimura 331/2        |

|-----------|---------|---------------------|

| 4,259,744 | 3/1981  | Junod et al 331/2   |

| 4,498,103 | 2/1985  | Aschwanden 375/120  |

| 4,510,461 | 4/1985  | Dickes et al 331/2  |

| 4,534,044 | 8/1985  | Funke et al 331/1 A |

| 4,547,736 | 10/1985 | Takeda 331/4        |

| 4,565,976 | 1/1986  | Campbell 375/87     |

| 4,580,101 | 4/1986  | Lax 375/81          |

| 4,590,602 | 5/1986  | Wolauer 375/120     |

| 4,809,068 | 2/1989  | Nagai 375/120       |

|           |         |                     |

| 4,847,876 | 7/1989 | Baumbach et al 375/120 |

|-----------|--------|------------------------|

| 4,908,841 | 3/1990 | Leis et al 375/81      |

| 4,933,959 | 6/1990 | Knechtel 375/120       |

#### OTHER PUBLICATIONS

Gardner, F. M., "Charge-Pump Phase-Lock Loops," *IEEE Transactions on Communications*, vol. Com-28, No. 11, pp. 1849-1858 (Nov. 1980).

Primary Examiner—Stephen Chin Attorney, Agent, or Firm—Townsend and Townsend Khourie and Crew

### [57] ABSTRACT

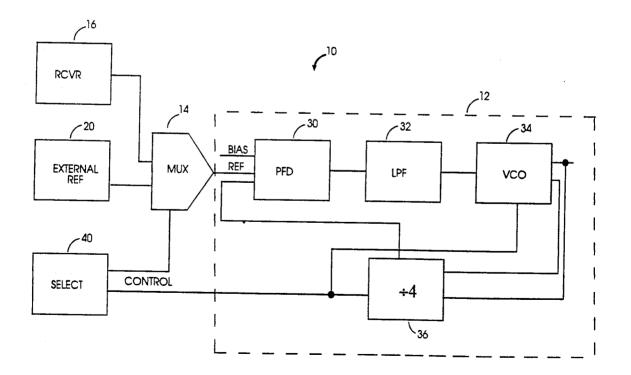

A bi-phase decoder for extraction of an embedded clock in a Manchester encoded signal operating at about ten megahertz. A phase-lock loop (PLL) includes a phase frequency detector and an interruptible voltage controlled oscillator (VCO). The PLL has a narrow bandwidth for stability to reduce effects of five megahertz components on clock extraction. The bi-phase decoder has a fast acquisition time to ensure frequency and phase lock during a preamble portion of an input data packet. A clock reference operates the PLL and the VCO at a nominal frequency of the embedded clock. Receipt of a data packet initiates interruption of the VCO operation to switch in the received data. The VCO resumes operation in phase with the received data packet and at about the proper frequency, therefore acquisition is fast. The VCO is designed to resume operation after operation at a particular phase to help in phase alignment.

#### 7 Claims, 7 Drawing Sheets